STMicroelectronics recently introduced its Stellar P3E MCU. The newest member of the Stellar P automotive MCU family, P3E, uniquely integrates a dedicated neural processing unit (NPU) alongside high-performance real-time control cores to bring AI acceleration to X-in-1 electronic control units (ECUs).

ST says the new device is the first automotive MCU with an embedded NPU accelerator.

AI Acceleration at the MCU Level

One of ST’s major selling points with the Stellar P3E is its Neural-ART Accelerator, an on-chip neural processing unit optimized for real-time inference. In contrast to DSP-based implementations that repurpose general-purpose compute cores for AI tasks, the Neural-ART block uses a data-flow architecture designed to minimize memory movement and reduce energy per inference.

According to ST, the accelerator can deliver up to 30 times greater AI efficiency than running neural models on traditional MCU cores, while achieving microsecond-level inference latency.

“What was very important for us was to offer an easy-to-use neural network processor that does not consume too much area, memory, or power,” said Yoann Foucher, ST's automotive MCU product strategy director.

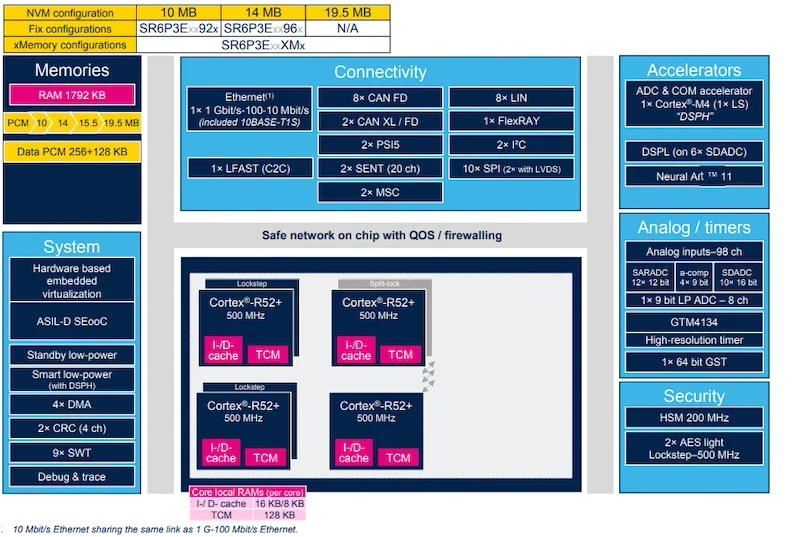

Stellar P3E block diagram.

The P3E supports an inference throughput of 80+ GOPS for suitable workloads, with optimized support for quantized integer models. The NPU operates independently of the Cortex-R52+ clusters and can be isolated at the memory and system levels to preserve determinism in hard real-time control loops, a key requirement for safety-critical automotive systems.

The architecture allows neural workloads such as classification, regression, and anomaly detection to be offloaded to the NPU, freeing the main cores to maintain motor-control and digital-power tasks. The Cortex-R52+ cluster itself delivers a CoreMark score exceeding 8,000 at 500 MHz, making it the highest-performing in its class, according to ST.

The cores support split-lock configurations, enabling dynamic trade-offs between maximum performance and redundancy. Designers can configure the system with four cores, two in lockstep, or with three cores all operating in lockstep, which meets ISO 26262 ASIL-D requirements.

xMemory PCM Scalable Nonvolatile Storage

The Stellar P3E incorporates ST’s proprietary xMemory, a phase-change memory (PCM)-based nonvolatile technology that replaces conventional embedded flash. The device supports up to 19.5 MB of on-chip nonvolatile memory, including up to 19 MB dedicated to code storage and 512 KB reserved for the hardware security module.

ST’s PCM technology.

ST says PCM provides roughly twice the density of traditional embedded flash, meaning larger code images and extensible software architectures without increasing die area proportionally.

“The xMemory actually is one part number that can cover any memory requirements,” said Davide Santo, ST's automotive MCU business unit senior director. “Our customers are not going to hit a memory ceiling, because we are providing enough memory to run multiple functions or even multiple updates as we go through the lifetime of the product.”

The P3E also supports an A/B swap mechanism for over-the-air (OTA) updates, allowing dual firmware images to coexist in memory to unlock features like rollback in the event of incomplete or failed updates. In addition to code NVM, the device integrates 384 KB of data NVM and up to 1,792 KB of SRAM for real-time execution and buffering. The memory subsystem is tightly coupled to the Cortex-R52+ cores through instruction and data caches and through tightly coupled memory (TCM).

Analog Density and High-Speed Networking for X-in-1 Architectures

The P3E’s peripheral set targets powertrain integration. The MCU integrates 12 separate 12-bit SAR ADCs, 10 independent 16-bit sigma-delta ADCs with embedded DSP processing, and multiple 9-bit comparators, providing more than 100 analog input channels. This density helps designers consolidate disparate functions into a single ECU, increasing functionality without sacrificing space.

An X-in-1 powertrain domain controller solution based on Stellar P3E.

Fabricated on ST’s 28-nm FD-SOI automotive-qualified process, the device also supports 1 Gbit/s Ethernet compliant with IEEE 802.3-2008, including 10BASE-T1S capability, along with CAN FD and CAN XL interfaces. To save power, it introduces enhanced smart low-power modes that allow selective subsystem activation when the vehicle is parked.

Availability and Outlook

The MCU is positioned for production in the fourth quarter of 2026.

“Consider Stellar P3E as the first step,” said Santo. “We expect even more to come in the future with even better innovations and more value to automotive designers.”

-

Tel

+86 180 2549 2789 -

Wechat

BOM

BOM Cart()

Cart() English

English Russia

Russia Korean

Korean